## **On-Chip Bus for SoC**

2013 - 2017

Ando Ki, Ph.D. (adki@future-ds.com)

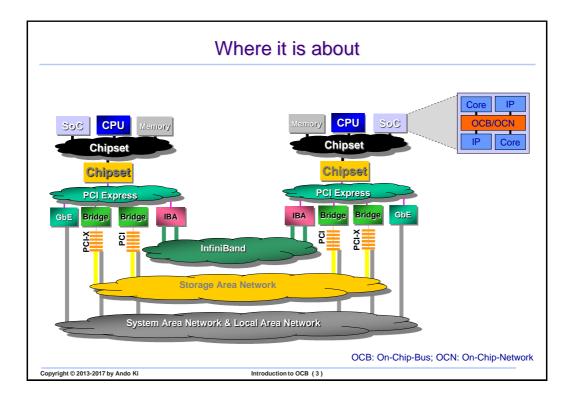

| Agenda                                                                                                                                                                                                                |                                                                                                          |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Where it is about</li> <li>What is on-chip bus</li> <li>Standard and/or de factor standard bus n ot for SoC</li> <li>Interconnect landscape not for SoC</li> <li>De factor standard buses for SoC</li> </ul> | <ul> <li>ARM AMBA</li> <li>IBM CoreConnect</li> <li>Altera Avalon</li> <li>OpenCores Wishbone</li> </ul> |  |  |

| Copyright © 2013-2017 by Ando Ki Introductio                                                                                                                                                                          | nto OCB (2)                                                                                              |  |  |

|                                                                                                                           | AMBA          | CoreConnect   | Wishbone          | Avalon         |

|---------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-------------------|----------------|

| owner                                                                                                                     | ARM           | IBM           | OpenCores         | Altera         |

| license Open and royalty-free, but license scheme is not clear free, but need agreement open/free, no license proprietary |               | proprietary   |                   |                |

| where                                                                                                                     | www.arm.com   | www.ibm.com   | www.opencores.org | www.altera.com |

| buses                                                                                                                     | AXI, AHB, APB | PLB, OPB, DCR |                   |                |

| arbitration central ce                                                                                                    |               | central       | central           | central        |

| clock                                                                                                                     | synchronous   | synchronous   | synchronous       | synchronous    |

|                                                                                                                           |               |               |                   |                |

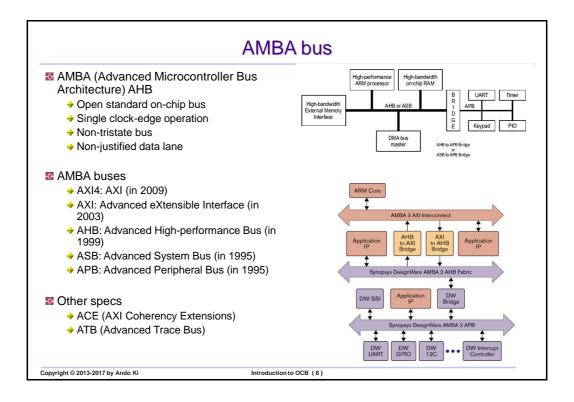

AMBA: Advanced Microcontroller Bus Architecture

Copyright © 2013-2017 by Ando Ki

Introduction to OCB (6)

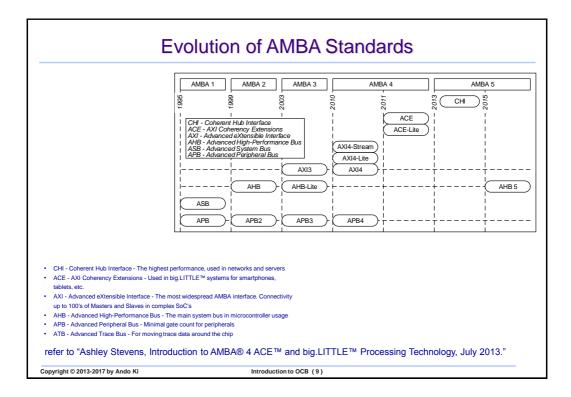

| AMBA 4 AXI AMBA 3 AXI AMBA 2 AHB |                                                                                                                                                                 | AMBA 2 AHB                                                                                                                                                                       |                |                                                                                                                                                                                                                                |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | an extension of AMBA 3 AXI<br>Burst length up to 256<br>Quality-of-service<br>Removal of lock transaction<br>Removal of write interleaving                      | channel architecture<br>registers slices<br>one address for burst up to 16<br>multiple outstanding bursts<br>out of order completion<br>data interleaving<br>low-power interface |                | burst transfers<br>pipelined operation<br>split transactions<br>single-cycle bus master handove<br>single-clock edge operation<br>multiple bus masters (up to 16)<br>two uni-directional 32-bit data<br>bus for read and write |

|                                  | AMBA 4 APB                                                                                                                                                      | AMBA 3 APB                                                                                                                                                                       |                | AMBA 2 APB                                                                                                                                                                                                                     |

| 開始                               | an extension of AMBA 3 APB<br>transaction protection (normal-<br>privileged, secure-nonsecure,<br>data-instruction)<br>Sparse data transfer (partial<br>access) | an extension of AMBA 2 APB<br>wait state supported<br>error response supported                                                                                                   | 22<br>22<br>23 | low power<br>latched address and control<br>simple interface<br>suitable for many peripherals                                                                                                                                  |

|                                  | AHB                                                  |  |  |  |

|----------------------------------|------------------------------------------------------|--|--|--|

|                                  |                                                      |  |  |  |

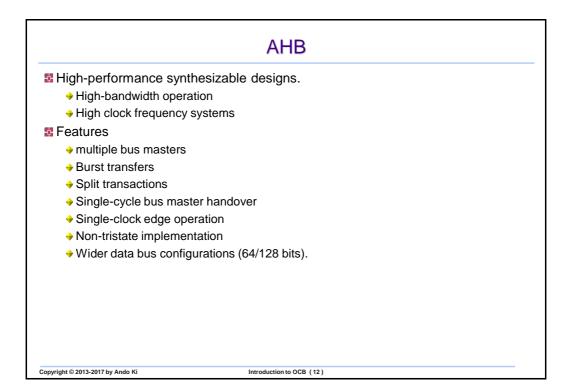

| busname                          | AMBA AHB (new generation bus)                        |  |  |  |

| data bus width                   | 32- 64- 128- 256-bit                                 |  |  |  |

| address bus width                | 32 bit                                               |  |  |  |

| architecture                     | (Multi) MASTER / (Multi) SLAVE                       |  |  |  |

|                                  | arbitration logic interface well defined             |  |  |  |

|                                  | Single cycle bus master handover possible            |  |  |  |

| data bus protocol                | Single READ/WRITE transfer                           |  |  |  |

|                                  | burst transfer (4 – 8 – 16 beats)                    |  |  |  |

|                                  | Pipelined                                            |  |  |  |

|                                  | split transactions supported                         |  |  |  |

|                                  | Byte/half-word/word transfer support                 |  |  |  |

| data ordering                    | No dynamic endianess                                 |  |  |  |

| timing                           | Synchronous, well defined timing specs               |  |  |  |

| interconnection                  | multiplexed implementation                           |  |  |  |

| supported                        | Non-tristate                                         |  |  |  |

| interconnections                 | Separate data read & write bus required              |  |  |  |

| technology                       | Technology independent                               |  |  |  |

|                                  | Reference: Overview Embedded Buses, Patrick Pelgrims |  |  |  |

| Copyright © 2013-2017 by Ando Ki | Introduction to OCB (13)                             |  |  |  |

|                                                     | APB                                                                        |

|-----------------------------------------------------|----------------------------------------------------------------------------|

| Low-power extensior                                 | to the system bus (AHB/ASB)                                                |

| Minimal power cons                                  | sumption                                                                   |

| Reduced interface                                   | complexity.                                                                |

| Local secondary bus                                 | that is encapsulated as a single AHB/ASB slave device                      |

| A slave module whi                                  | ch handles local peripheral bus.                                           |

| <ul> <li>An APB bridge conv<br/>the APB.</li> </ul> | verts AHB or ASB transfers into a suitable format for the slave devices on |

| The bridge provides                                 | s latching of all address, data and control signals                        |

| E Features                                          |                                                                            |

| Low bandwidth                                       |                                                                            |

| Unpipelined bus int                                 | erface.                                                                    |

| address and contr                                   | ol valid throughout the access (unpipelined)                               |

| All signal transitions                              | s are only related to the rising edge of the clock                         |

| <ul> <li>Zero-power interfac<br/>use)</li> </ul>    | e during non-peripheral bus activity (peripheral bus is static when not in |

| Timing can be provi                                 | ded by decode with strobe timing (unclocked interface)                     |

| Write data valid for                                | the whole access                                                           |

| allowing glitch-free                                | e transparent latch implementations).                                      |

|                                                     |                                                                            |

|                                                     |                                                                            |

| pyright © 2013-2017 by Ando Ki                      | Introduction to OCB (14)                                                   |

| busname                                | AMBA APB                                            |    |  |

|----------------------------------------|-----------------------------------------------------|----|--|

| data bus width                         | 8-16-32-bit                                         |    |  |

| address bus width                      | 32 bit                                              |    |  |

| tagging                                | No tagging                                          |    |  |

| architecture                           | (Single) MASTER (bridge) / (Multi) SLAVE            |    |  |

|                                        | No arbitration logic needed                         |    |  |

| data bus protocol                      | 2 cycle single READ/WRITE transfer                  |    |  |

|                                        | No burst transfer                                   |    |  |

|                                        | Non-Pipelined                                       |    |  |

| timing                                 | Synchronous, well defined timing specs              |    |  |

| interconnection                        | Not defined                                         |    |  |

| supported Non-tristate-bus recommended |                                                     |    |  |

| interconnections                       | Separate data read & write bus recommended          |    |  |

| technology                             | Technology independent                              |    |  |

| power                                  | Zero power when not in use                          |    |  |

|                                        | Reference: Overview Embedded Buses, Patrick Pelgrin | ns |  |

| Age                                                                                                                                                                                                                                                                                                                                                                          | enda                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| <ul> <li>Where it is about</li> <li>What is on-chip bus</li> <li>Standard and/or de factor standard bus n ot for SoC</li> <li>Interconnect landscape not for SoC</li> <li>De factor standard buses for SoC</li> <li>Arbitration</li> <li>Burst transfers</li> <li>Pipelined and split transfers</li> <li>Data ordering</li> <li>Justificatin or not for data lane</li> </ul> | <ul> <li>ARM AMBA</li> <li>IBM CoreConnect</li> <li>Altera Avalon</li> <li>OpenCores Wishbone</li> </ul> |

| Copyright © 2013-2017 by Ando Ki Introduction                                                                                                                                                                                                                                                                                                                                | to OCB (16)                                                                                              |

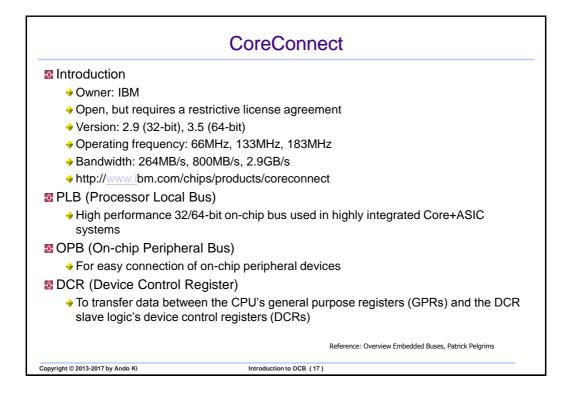

|                                             | CoreConnect                                                                                                                                                                                  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trough and has a good systems, thus raising | pplete and versatile solution, as it is well thought<br>d architecture. It clearly targets high performance<br>the complexity and offering many features that<br>mple embedded applications. |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             |                                                                                                                                                                                              |

|                                             | Reference: Overview Embedded Buses, Patrick Pelgrims                                                                                                                                         |

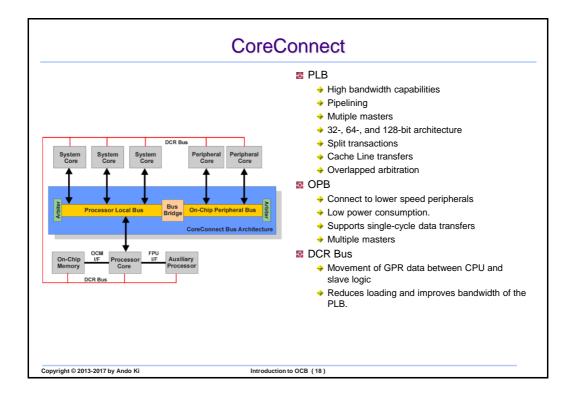

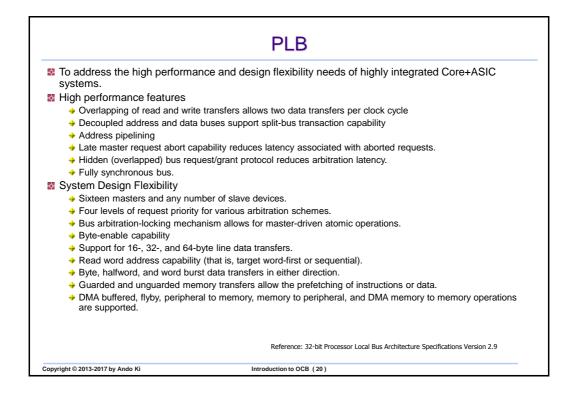

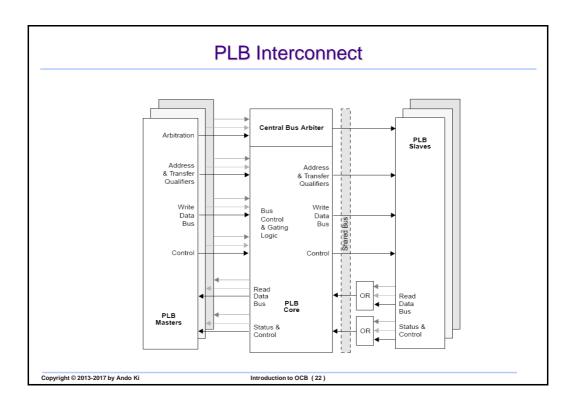

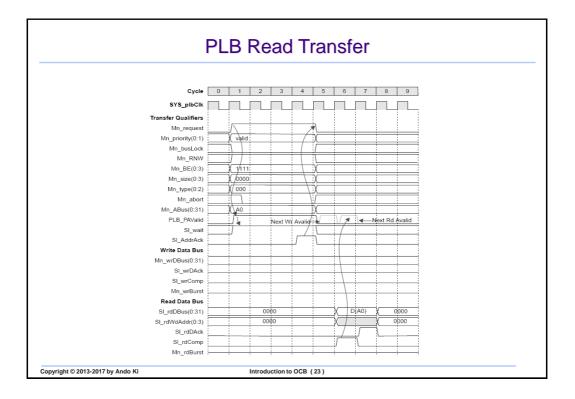

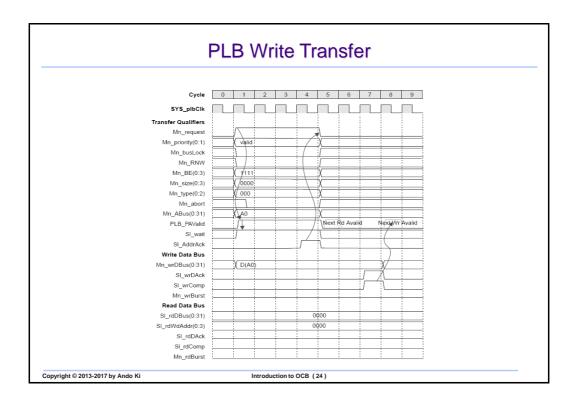

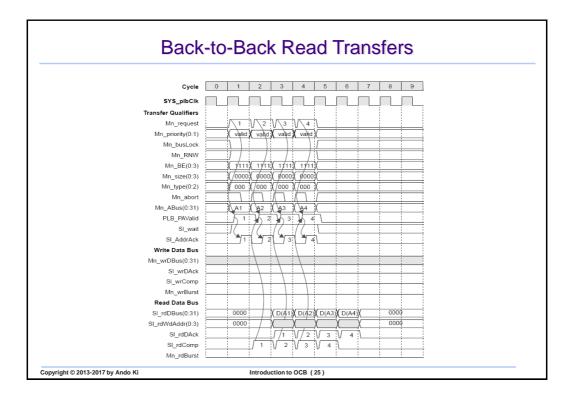

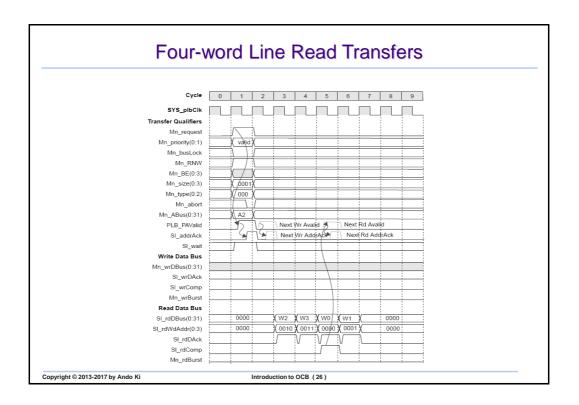

|                                             | PLB                                                |  |  |

|---------------------------------------------|----------------------------------------------------|--|--|

|                                             |                                                    |  |  |

| busname                                     | CORECONNECT PLB                                    |  |  |

| data bus width                              | 32-, 64-, 128-,256-bit                             |  |  |

| address bus width                           | 32-bit                                             |  |  |

|                                             | (with address pipelining, reducing latency)        |  |  |

| architecture                                | (Multi) MASTER [MAX 8]/ (Multi) SLAVE              |  |  |

|                                             | Arbiters with different priority schemes available |  |  |

|                                             | as soft-core                                       |  |  |

| data bus protocol                           | Single READ/WRITE transfer                         |  |  |

|                                             | Overlapped READ & WRITE (2transfers/cycle)         |  |  |

|                                             | Burst transfer (16-64 byte bursts)                 |  |  |

|                                             | pipelining                                         |  |  |

|                                             | Split transfer support                             |  |  |

|                                             | Special DMA modes (flyby,)                         |  |  |

| timing                                      | Fully synchronous                                  |  |  |

| interconnection                             | multiplexed implementation (=crossbar switch)      |  |  |

| supported                                   | Non tri-state                                      |  |  |

| interconnections                            | Separate data read & write bus                     |  |  |

| technology                                  | Technology independent                             |  |  |

|                                             | Reference: Overview Embedded Buses, Patrick Pelgu  |  |  |

| 13-2017 by Ando Ki Introduction to OCB (21) |                                                    |  |  |

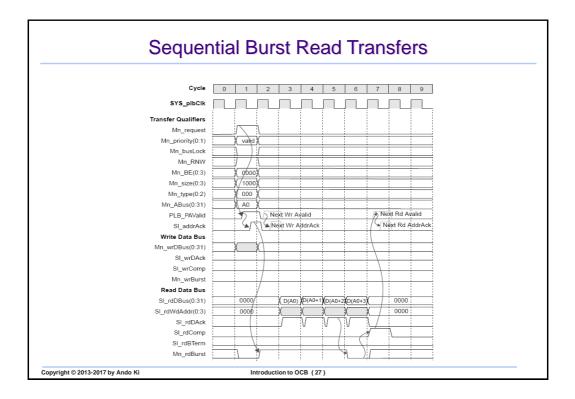

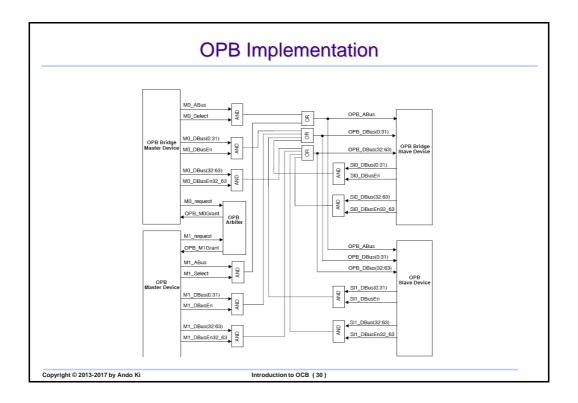

|      | OPB                                                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------|

| ÷    | For easy connection of on-chip peripheral devices                                                                                     |

| ¢    | It is not intended to connect directly to the processor core.                                                                         |

|      | The processor core can access the slave peripherals on this bus through the PLB to OPB bridge unit                                    |

| ÷    | Features                                                                                                                              |

|      | Up to a 64-bit address bus / 32-bit or 64-bit data bus implementations                                                                |

|      | ♦ Fully synchronous                                                                                                                   |

|      | Provides support for 8-bit, 16-bit, 32-bit, and 64-bit slaves / 32-bit and 64-bit masters                                             |

|      | Oynamic bus sizing; byte, halfword, fullword, and doubleword transfers                                                                |

|      | Optional Byte Enable support                                                                                                          |

|      | Uses a distributed multiplexer method                                                                                                 |

|      | Byte and halfword duplication for byte and halfword transfers     Single grade transfer of data between ODB has meeter and ODB algues |

|      | <ul> <li>Single cycle transfer of data between OPB bus master and OPB slaves</li> <li>Sequential address protocol support</li> </ul>  |

|      | <ul> <li>A 16-cycle fixed bus timeout provided by the OPB arbiter</li> </ul>                                                          |

|      | <ul> <li>OPB slave is capable of disabiling the fixed timeout counter to suspend bus timeout error</li> </ul>                         |

|      | Support for multiple OPB bus masters                                                                                                  |

|      | <ul> <li>Bus parking for reduced latency</li> </ul>                                                                                   |

|      | OPB masters may lock the OPB bus arbitration                                                                                          |

|      | <ul> <li>OPB slaves capable of requesting retry to break possible arbitration deadlock</li> </ul>                                     |

|      | <ul> <li>Bus arbitration overlapped with last cycle of bus transfers</li> </ul>                                                       |

|      |                                                                                                                                       |

|      | Reference: On-Chip Peripheral Bus Architecture Specifications Version 2.1                                                             |

| opvr | ight © 2013-2017 by Ando Ki Introduction to OCB (28)                                                                                  |

| busname                                          | CORECONNECT OPB                                    |

|--------------------------------------------------|----------------------------------------------------|

| data bus width                                   | 8-, 16-,32-bit                                     |

| address bus width                                | 32-bit                                             |

| architecture                                     | (Multi) MASTER / (Multi) SLAVE                     |

|                                                  | Arbiters with different priority schemes available |

|                                                  | as soft-core                                       |

|                                                  | Dynamic bus sizing possible                        |

| data bus protocol                                | Single READ/WRITE transfer                         |

|                                                  | Burst support                                      |

|                                                  | Retry support                                      |

|                                                  | Single byte, half word or word transfers           |

|                                                  | DMA support                                        |

| timing                                           | Fully synchronous                                  |

| interconnection                                  | multiplexed implementation                         |

| supported                                        | Non tri-state                                      |

|                                                  | Separate data read & write bus                     |

| technology                                       | Technology independent                             |

|                                                  |                                                    |

| interconnection<br>supported<br>interconnections | Non tri-state<br>Separate data read & write bus    |

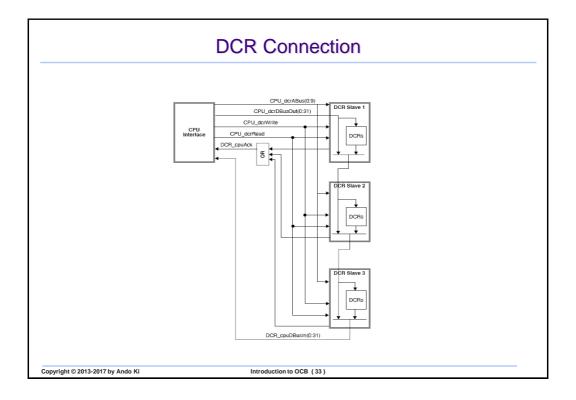

|                                                                                                                                                                                                                                                                                                                                                                                                      | DCR Bus                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>device control registers (DCRs)</li> <li>To remove configuration registers from</li> <li>To reduces loading</li> <li>To improves bandwidth of the process</li> <li>Fully synchronous</li> <li>The slower clock's rising edge always</li> <li>The DCR bus is typically implemente</li> <li>Each sub-unit not only has a path to p</li> <li>but also has a path which bypasses its</li> </ul> | sor local bus.<br>• corresponds to the faster clock's rising edge.<br>• d as a distributed mux<br>• blace its own DCRs on the CPU's DCR read path<br>• s DCRs and places another unit's DCRs on the CPU's DCR read path.<br>• exist architecturally outside the processor core.<br>• instruction<br>dcr) instructions.<br>• s<br>• rs extendable by slave or master<br>onous transfers<br>• rslower than master |

|                                                                                                                                                                                                                                                                                                                                                                                                      | Reference: 32-Bit Device Control Register Bus Architecture Specifications Version 2.9                                                                                                                                                                                                                                                                                                                           |

| Copyright © 2013-2017 by Ando Ki                                                                                                                                                                                                                                                                                                                                                                     | Introduction to OCB (31)                                                                                                                                                                                                                                                                                                                                                                                        |

|                                 | DCR Bus                                        |          |  |  |  |  |  |

|---------------------------------|------------------------------------------------|----------|--|--|--|--|--|

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

| busname                         | CORECONNECT DCR                                |          |  |  |  |  |  |

| data bus width                  | 32-bit                                         |          |  |  |  |  |  |

| address bus width               | 10-bit                                         |          |  |  |  |  |  |

| Interconnection                 | multiplexed implementation                     |          |  |  |  |  |  |

| purpose                         | Transfer data between the CPU's general        |          |  |  |  |  |  |

|                                 | purpose registers (GPR) and other (peripheral) |          |  |  |  |  |  |

|                                 | registers, not meant for real data transfers   |          |  |  |  |  |  |

|                                 | Designed to reduce load on PLB and OPB         |          |  |  |  |  |  |

|                                 | <u> </u>                                       |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

|                                 | Reference: Overview Embedded Buses, Patrick    | Pelgrims |  |  |  |  |  |

|                                 |                                                |          |  |  |  |  |  |

| opyright © 2013-2017 by Ando Ki | Introduction to OCB (32)                       |          |  |  |  |  |  |

| <ul> <li>Where it is about</li> <li>What is on-chip bus</li> <li>Standard and/or de factor standard bus n<br/>ot for SoC</li> <li>Interconnect landscape not for SoC</li> <li>De factor standard buses for SoC</li> <li>Arbitration</li> <li>Burst transfers</li> <li>Pipelined and split transfers</li> <li>Data ordering</li> <li>Justificatin or not for data lane</li> </ul> | Agenda                                                                                                                                                                                                                                                                                                 |                                                            |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                  | <ul> <li>What is on-chip bus</li> <li>Standard and/or de factor standard bus n ot for SoC</li> <li>Interconnect landscape not for SoC</li> <li>De factor standard buses for SoC</li> <li>Arbitration</li> <li>Burst transfers</li> <li>Pipelined and split transfers</li> <li>Data ordering</li> </ul> | <ul> <li>IBM CoreConnect</li> <li>Altera Avalon</li> </ul> |  |  |  |  |  |  |  |  |  |  |

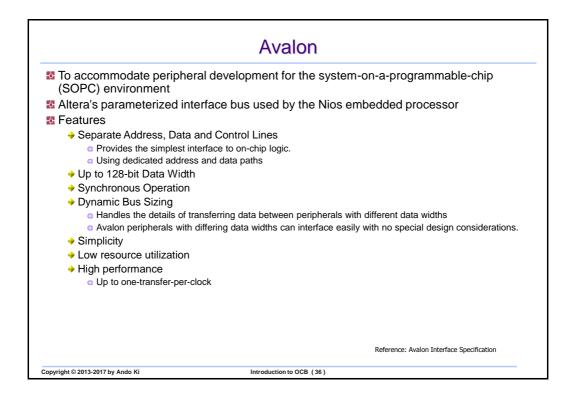

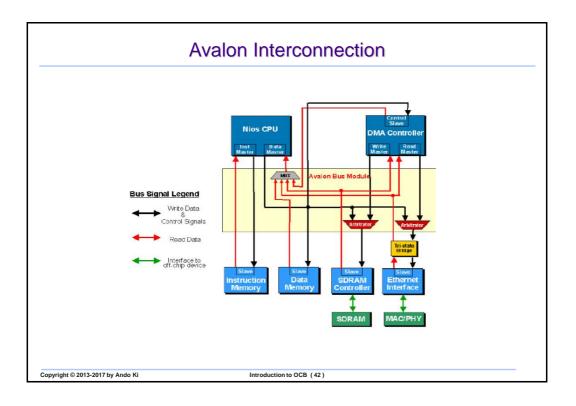

| Busname           | AVALON                                          |

|-------------------|-------------------------------------------------|

| data bus width    | 8. 16 or 32 bits                                |

| address bus width | 32-bit                                          |

| architecture      | multi-master / multi slave                      |

|                   | multi-master arbitration logic                  |

| specific features | interrupt-priority assignment                   |

| opeenie ieuteree  | wait-state generation                           |

| -                 | read & write transfers with latency             |

| data bus protocol | one or more bus cycles                          |

| •                 | streaming transfers (burst)                     |

|                   | single byte, half word or word transfers        |

|                   | fixed- or peripheral-controlled wait states     |

| -                 | with or without setup time                      |

| timing            | all signals synchronous with Avalon clock       |

|                   | simple timing behavior                          |

| size              | minimal FPGA resources                          |

| supported         | separate address, data and control lines        |

| interconnections  | tri-state signals (external) only with bridge   |

| technology        | Altera Avalon can only be implemented on        |

|                   | Altera devices using SOPC Builder               |

|                   | Reference: Overview Embedded Buses, Patrick Pel |

| ndo Ki            | Introduction to OCB (37)                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | WISHBONE                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Simple, compact, lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ogical IP core hardware interfaces                                                                        |

| Variable core interc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | connection methods                                                                                        |

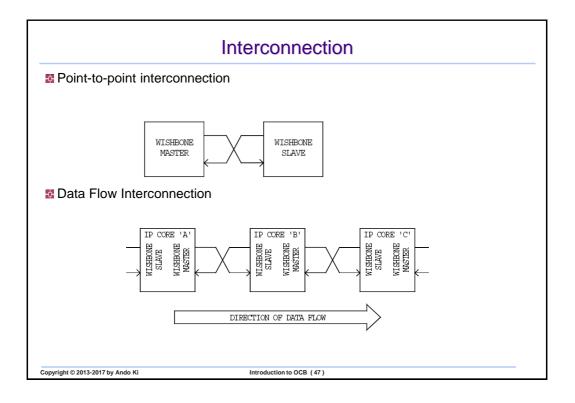

| Point-to-point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |

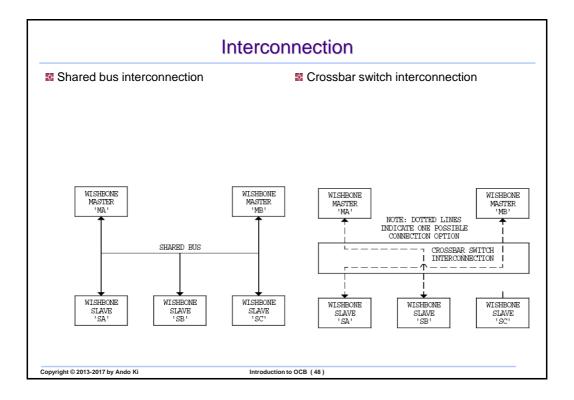

| Shared bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |

| Crossbar switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                           |

| Data flow interco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nnection                                                                                                  |

| switched fabric in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | terconnections                                                                                            |

| Off chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                           |

| User-defined tags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                           |

| Applying information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tion to an address bus, a data bus or a bus cycle.                                                        |

| 🔶 Helpful when mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | difying a bus cycle to identify information such as:                                                      |

| Data transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |

| Parity or error of a second |                                                                                                           |

| <ul> <li>Interrupt vector</li> <li>Casha control of</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                           |

| Cache control o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                           |

| Arbitration method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | blogy is defined by the end user                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Reference: WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores Revision: B.3 |