|                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Agenda                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

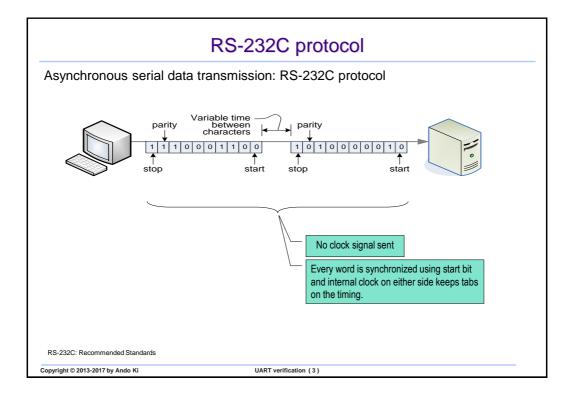

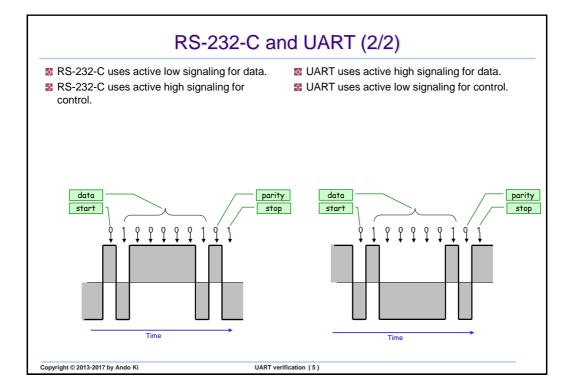

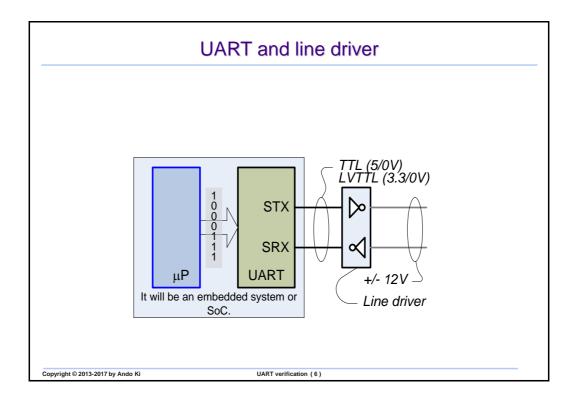

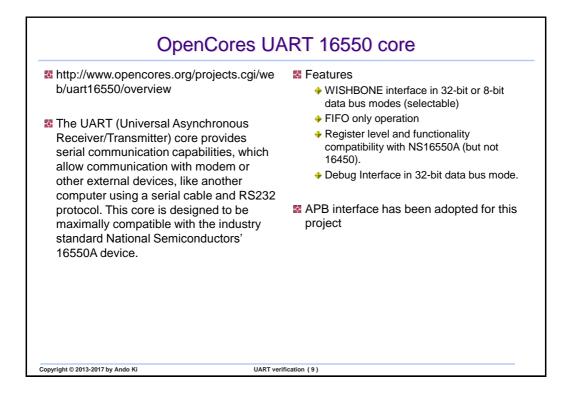

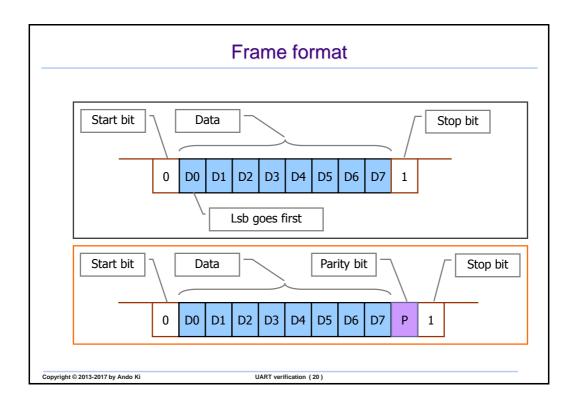

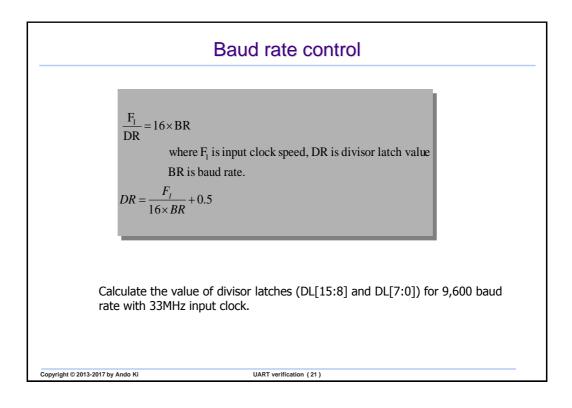

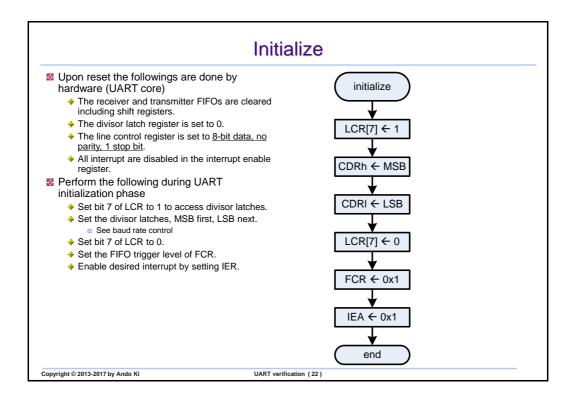

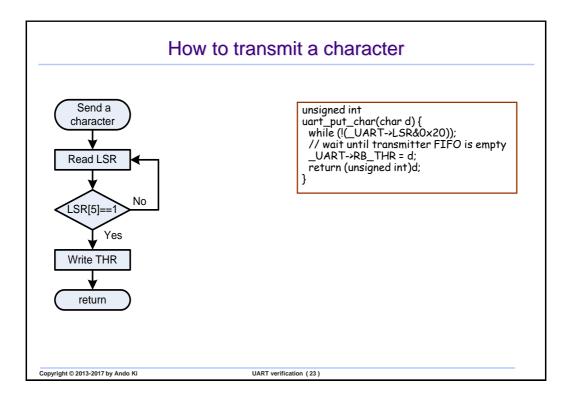

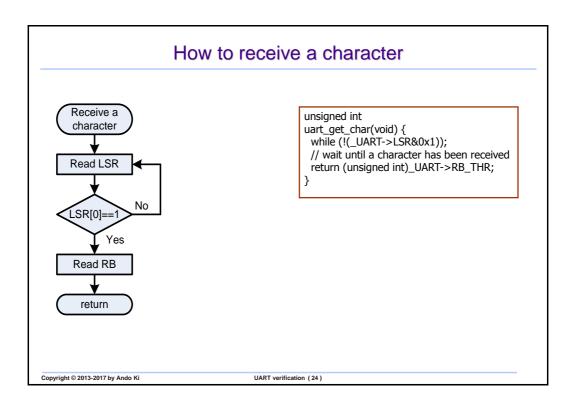

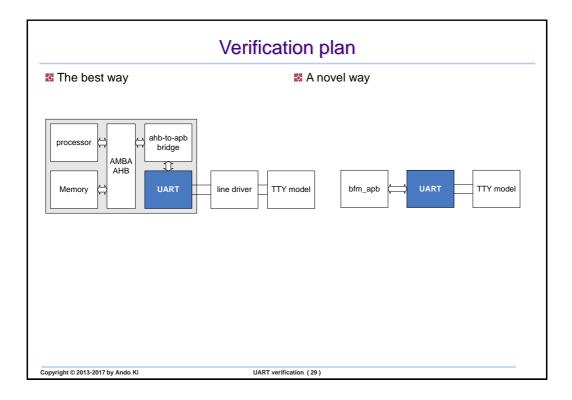

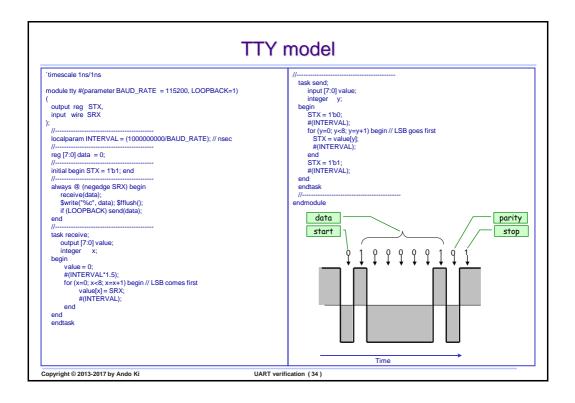

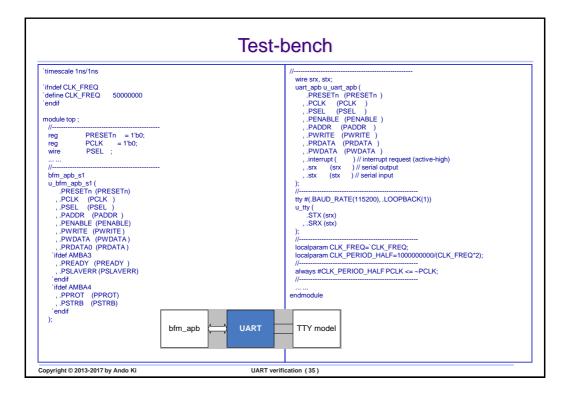

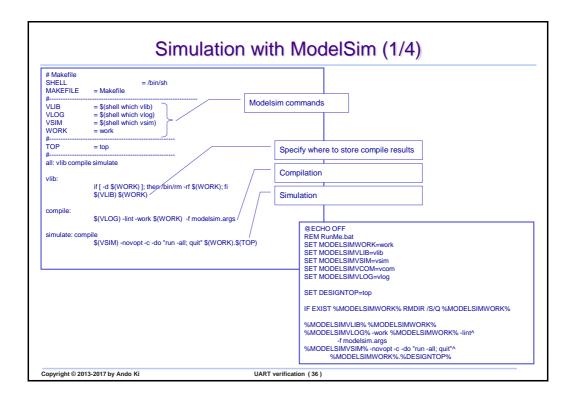

| <ul> <li>RS-232C protocol</li> <li>RS-232C and UART</li> <li>UART and line driver</li> <li>Type of UARTS</li> <li>OpenCores UART 16550 core</li> <li>Frame format</li> <li>Baud rate control</li> <li>Initialize</li> <li>How to transmit a character</li> <li>How to receive a character</li> <li>UART HW spec.</li> <li>How to control HW through SW</li> <li>Verification plan</li> <li>APB BFM and APB tasks</li> <li>TTY model</li> <li>Simulation</li> </ul> |                       |

| Copyright © 2013-2017 by Ando Ki                                                                                                                                                                                                                                                                                                                                                                                                                                   | UART verification (2) |

|        | remarks                                                                                                                                                                        |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

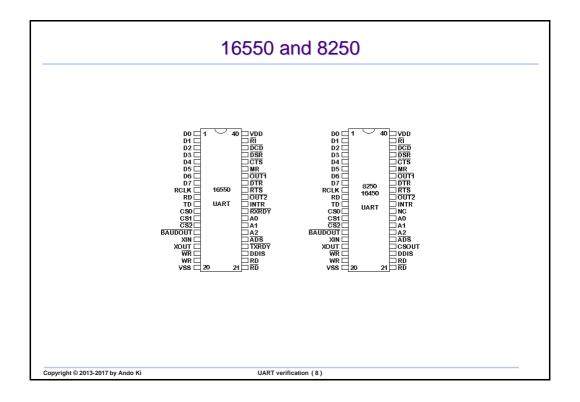

| 8250   | The first UART in this line. It doesn't contain any scratch registers. 8250A is a modernized version of 8250, its bus operating speed is very fast.                            |

| 8250A  | The bus operating speed of this UART is greater than 8250's. It is used in the same way as 16450 in the sphere of software.                                                    |

| 8250B  | Very similar to that of the 8250 UART.                                                                                                                                         |

| 16450  | Used in AT's (Improved bus speed over 8250's). Works stable at 38.4KBPS. Widespread today.                                                                                     |

| 16550  | This line is the first generation of buffered UART. This line has 16-byte buffer, however it doesn't work and is replaced with the 16550A.                                     |

| 16550A | This line is the most widespread UART version used for high-speed connection of moderns with 14.4KBPS and 28.8KBPS rates. They made sure the FIFO buffers worked on this UART. |

| 16650  | New generation of UART. Contains 32 bytes of FIFO, programmed register of X-On/X-Off characters and supports power management.                                                 |

| 16750  | Produced by Texas Instruments. Contains 64-byte FIFO buffer.                                                                                                                   |

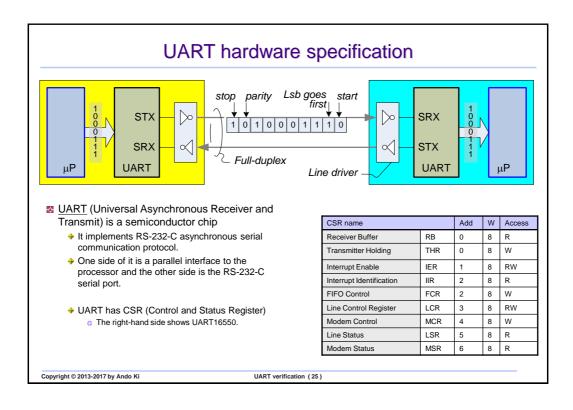

| Name                            |     | Addr | W | V Access | Description                                  |  |

|---------------------------------|-----|------|---|----------|----------------------------------------------|--|

| Receiver Buffer                 | RB  | 0    | 8 | R        | Receiver FIFO output                         |  |

| Transmitter Holding<br>Register | THR | 0    | 8 | W        | Transmit FIFO input                          |  |

| Interrupt Enable                | IER | 1    | 8 | RW       | Enable/Mask interrupts generated by the UART |  |

| Interrupt Identification        | IIR | 2    | 8 | R        | Get interrupt information                    |  |

| FIFO Control                    | FCR | 2    | 8 | W        | Control FIFO options                         |  |

| Line Control Register           | LCR | 3    | 8 | RW       | Control connection                           |  |

| Modem Control                   | MCR | 4    | 8 | W        | Controls modem                               |  |

| Line Status                     | LSR | 5    | 8 | R        | Status information                           |  |

| Modem Status                    | MSR | 6    | 8 | R        | Modem Status                                 |  |

Copyright © 2013-2017 by Ando Ki

UART verification (10)

| Name                                       |      | Addr | W | Access | Description                  |

|--------------------------------------------|------|------|---|--------|------------------------------|

| Divisor Latch Byte 1<br>(LSB)              | CDRI | 0    | 8 | RW     | The LSB of the divisor latch |

| Divisor Latch Byte 2                       | CDRh | 1    | 8 | RW     | The MSB of the divisor latch |

| Two clock divisor re<br>The CDR is accesse |      |      |   |        |                              |

|                                            |      |      |   |        |                              |

|                                            |      |      |   |        |                              |

|                                            |      |      |   |        |                              |

|                                            |      |      |   |        |                              |

| Bit # | Access | Description                                                                     |                  |

|-------|--------|---------------------------------------------------------------------------------|------------------|

| 0     | RW     | Received Data available interrupt<br>'0' – disabled<br>'1' – enabled            |                  |

| 1     | RW     | Transmitter Holding Register empty interrupt<br>'0' – disabled<br>'1' – enabled |                  |

| 2     | RW     | Receiver Line Status Interrupt<br>'0' – disabled<br>'1' – enabled               |                  |

| 3     | RW     | Modem Status Interrupt<br>'0' – disabled<br>'1' – enabled                       |                  |

| 7-4   | RW     | Reserved. Should be logic '0'.                                                  |                  |

|       |        |                                                                                 | Reset value: 001 |

| bit |   | pr Interrupt Type |     | Interrupt Type                           | Interrupt Source                                                                                                                         | Interrupt Reset Control                                           |

|-----|---|-------------------|-----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 3   | 2 | 1                 | ] i |                                          |                                                                                                                                          |                                                                   |

| 0   | 1 | 1                 | 1   | Receiver Line<br>Status                  | Parity, Overrun or Framing errors or<br>Break Interrupt                                                                                  | Reading the Line Status<br>Register                               |

| 0   | 1 | 0                 | 2   | Receiver Data available                  | FIFO trigger level reached                                                                                                               | FIFO drops below trigger level                                    |

| 1   | 1 | 0                 | 2   | Timeout Indication                       | There's at least 1 character in the FIFO<br>but no character has been input to the<br>FIFO or read from it for the last 4 Char<br>times. | Reading from the FIFO<br>(Receiver Buffer Register)               |

| 0   | 0 | 1                 | 3   | Transmitter<br>Holding Register<br>empty | Transmitter Holding Register Empty                                                                                                       | Writing to the Transmitter<br>Holding Register or reading<br>IIR. |

| 0   | 0 | 0                 | 4   | Modem Status                             | CTS, DSR, RI or DCD.                                                                                                                     | Reading the Modem status register.                                |

|     |   |                   |     |                                          |                                                                                                                                          | Reset value; C                                                    |

| Bit # | Access | Description                                                                                                                                                       |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | W      | Ignored (Used to enable FIFOs in NS16550D). Since this UART only supports FIFO mode, this bit is ignored.                                                         |

| 1     | W      | Writing a '1' to bit 1 clears the Receiver FIFO and resets its logic. But it doesn't clear the shift register, i.e. receiving of the current character continues. |

| 2     | W      | Writing a '1' to bit 2 clears the Transmitter FIFO and resets its logic. The shift register is not cleared, i.e. transmitting of the current character continues. |

| 5-3   | W      | Ignored                                                                                                                                                           |

| 7-6   | W      | Define the Receiver FIFO Interrupt trigger level<br>'00' – 1 byte<br>'01' – 4 bytes<br>'10' – 8 bytes<br>'11' – 14 bytes                                          |

Reset value: COh

Copyright © 2013-2017 by Ando Ki

UART verification (14)

| Bit # | Access | Description                                                                                                                                                                                                                                                              |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0   | RW     | Select number of bits in each character<br>'00' – 5 bits; '01' – 6 bits; '10' – 7 bits; '11' – 8 bits                                                                                                                                                                    |

| 2     | RW     | Specify the number of generated stop bits<br>'0' – 1 stop bit<br>'1' – 1.5 stop bits when 5-bit character length selected and<br>2 bits otherwise<br>Note that the receiver always checks the first stop bit only.                                                       |

| 3     | RW     | Parity Enable<br>'0' – No parity<br>'1' – Parity bit is generated on each outgoing character and<br>is checked on each incoming one.                                                                                                                                     |

| 4     | RW     | Even Parity select<br>'0' – Odd number of '1' is transmitted and checked in each word (data and<br>parity combined). In other words, if the data has an even number of '1' in it<br>then the parity bit is '1'.<br>'1' – Even number of '1' is transmitted in each word. |

| ransmitted and checked as<br>ity bit is transmitted and |

|---------------------------------------------------------|

|                                                         |

| state).                                                 |

|                                                         |

| k                                                       |

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | R      | Data Ready (DR) indicator.<br>'0' – No characters in the FIFO<br>'1' – At least one character has been received and is in the FIFO.                                                                                                                                                                                                                                                                |

| 1     | R      | Overrun Error (OE) indicator<br>'1' – If the FIFO is full and another character has been received in the<br>receiver shift register. If another character is starting to arrive, it will<br>overwrite the data in the shift register but the FIFO will remain intact. The bit<br>is cleared upon reading from the register. Generates Receiver Line Status<br>interrupt.<br>'0' – No overrun state |

| 2     | R      | Parity Error (PE) indicator<br>'1' – The character that is currently at the top of the FIFO has been received<br>with parity error. The bit is cleared upon reading from the register.<br>Generates Receiver Line Status interrupt.<br>'0' – No parity error in the current character                                                                                                              |

| Bit # | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3     | R      | <ul> <li>Framing Error (FE) indicator</li> <li>'1' – The received character at the top of the FIFO did not have a valid stop bit. Of course, generally, it might be that all the following data is corrupt. The bit is cleared upon reading from the register. Generates Receiver Line Status interrupt.</li> <li>'0' – No framing error in the current character</li> </ul>                                                                                                                                    |

| 4     | R      | Break Interrupt (BI) indicator<br>'1' –A break condition has been reached in the current character. The break<br>occurs when the line is held in logic 0 for a time of one character (start bit +<br>data + parity + stop bit). In that case, one zero character enters the FIFO<br>and the UART waits for a valid start bit to receive next character. The bit is<br>cleared upon reading from the register. Generates Receiver Line Status<br>interrupt.<br>'0' – No break condition in the current character |

| Bit # | Access | Description                                                                                                                                                                                                                  |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | R      | Transmit FIFO is empty.<br>'1' – The transmitter FIFO is empty. Generates Transmitter Holding Register<br>Empty interrupt. The bit is cleared when data is being been written to the<br>transmitter FIFO.<br>'0' – Otherwise |

| 6     | R      | Transmitter Empty indicator.<br>'1' – Both the transmitter FIFO and transmitter shift register are empty. The<br>bit is cleared when data is being been written to the transmitter FIFO.<br>'0' – Otherwise                  |

| 7     | R      | <ul> <li>'1' – At least one parity error, framing error or break indications have been received and are inside the FIFO. The bit is cleared upon reading from the register.</li> <li>'0' – Otherwise.</li> </ul>             |

|       |        | 5                                                                                                                                                                                                                            |

|       |        |                                                                                                                                                                                                                              |

| APB BFM: module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------------|--|

| timescale 1ns/1ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                          |  |

| <pre>nodule bfm_apb_s1 #(parameter P_ADDR_START0 = 16'h0000, P_ADDR_SIZE0 = 16'h00 input wire PCLK , output reg PSEL , output reg PSEL , output reg PENABLE , output reg PENABLE , output reg PINABLE , output reg [31:0] PVDATA , input wire [31:0] PVDATA , input wire [31:0] PVDATA , input wire [31:0] PRDATA0 ; reg [31:0] freq; real stamp_x, stamp_y, delta; initial begin PSEL = 11b0; PADDR = -32:h0; PPNABLE = 11b0; PVMAITE = 1'b0; PVMAITA = -32:h0; PPROT = 3'h0; PSTRB = 4th0; wait (PRESETn==150); Wait (PRESETn==</pre> |  | alculate frequency       |  |

| (e) (posedge PCLK); stamp_y = stamp_y, stamp_y, enal = stamp_y = stamp_y, (e) (negdege PCLK); stamp_y, (e) (freq = 1000000000/delta; repeat (3) @ (posedge PCLK); uart_test(freq, 115200); repeat (5) @ (posedge PCLK); \$finish(2); end                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  | II UART testing scenario |  |

| nteger err;<br>//                                                                                                                                                                                                                                                                                                                                                                               |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ,<br>ask uart_test;<br>input [31:0] freq;<br>input [31:0] baud;<br>reg [7:0] dat;                                                                                                                                                                                                                                                                                                               |                     |

| integer idx;                                                                                                                                                                                                                                                                                                                                                                                    | initialize UART     |

| begin<br>err = 0;<br>//                                                                                                                                                                                                                                                                                                                                                                         |                     |

| )/-init_uart(freq.// input [31:0] frea;<br>, baud // input [31:0] baud<br>);                                                                                                                                                                                                                                                                                                                    | Send a character    |

| //<br>for (idx="A"; idx<="Z"; idx = idx + 1) begin                                                                                                                                                                                                                                                                                                                                              | Receive a character |

| <pre>send_a_character(idx[7:0]);<br/>receive_a_character(idx];<br/>if (dat&gt;=8h208&amp;dat&lt;=8h7E)<br/>\$display(\$time,,"%m 0x%x(%c) received!", dat, dat);<br/>else<br/>\$display(\$time,,"%m 0x%x received!", dat);<br/>if (idx[7:0]!==dat) begin<br/>err = err + 1;<br/>\$display(\$time,,"%m ERROR 0x%x received, but 0x%x expected",<br/>dat, idx[7:0]);<br/>end<br/>end<br/>//</pre> |                     |

| if (err==0) \$display(\$time,,"%m test OK*);<br>end<br>endtask                                                                                                                                                                                                                                                                                                                                  | APB bus tasks       |

| Inclusk<br>/                                                                                                                                                                                                                                                                                                                                                                                    | UART handling tasks |

| // U16550 CSR address<br>localparam RB_THR =0<br>, IER =4<br>, IIR_FCR =8<br>, LCR =12 (initialize)                 |                   | UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} , MCR = 16 \\ , LSR = 20 \\ , MSR = 24; \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ |                   | am RB_THR =0<br>ER =4<br>R_FCR =8<br>CR =12<br>CR =16<br>SR =20;<br>Initialize UART CP<br>[31:0] freq;<br>[31:0] baud;<br>[31:0] baud;<br>[31:0] di;<br>write(LCR, 32h83, 4);<br>write(LCR, 32h03, 4);<br>write(L |

| //                                                                                                                  | )<br>]∙<br>]<br>) | d_a_character;         Send a character         dr           [31:0] tmp;         Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BFM APB tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| <pre>task apb_write;<br/>input [31:0] dadr;<br/>input [31:0] dadr;<br/>input [2:0] size;<br/>begin<br/>@ (posedge PCLK);<br/>PADDR &lt;= #1 dadr;<br/>PWRITE &lt;= #1 1'b1; //decoder(addr);<br/>PWDATA &lt;= #1 data;<br/>PSTRB &lt;= #1 get_pstrob(addr,size);<br/>@ (posedge PCLK);<br/>while (get_pready(addr)==1'b0) @ (posedge PCLK);<br/>'ifindet LOW_POWER<br/>PADDR &lt;= #1 32'h0;<br/>PWDATA &lt;= #1 1'b0;<br/>PWDATA &lt;= #1 1'b0;<br/>PWDATA &lt;= #1 1'b0;<br/>PENABLE &lt;= #1 1'b0;<br/>reindf<br/>PSLL &lt;= #1 1'b0;<br/>if (get_pstverr(addr)==1'b1) \$display(\$time,,"%m PSLVERR");<br/>endtask<br/>//</pre> | <pre>//</pre>     |  |

| Copyright © 2013-2017 by Ando Ki UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | verification (33) |  |

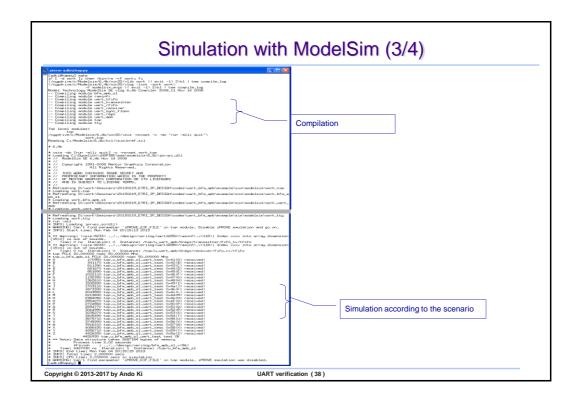

| //bench/verilog/top.v<br>//bench/verilog/tty.v             |  |  |

|------------------------------------------------------------|--|--|

| incdir+//bench/verilog<br>//bench/verilog/top.v            |  |  |

|                                                            |  |  |

| `ifndef_SIM_DEFINE_V_ sim_define.v<br>`define_SIM_DEFNE_V_ |  |  |

| //                                                         |  |  |

| define CLK_FREQ 50000000<br>`define MEM_DELAY 0            |  |  |

| 'endif                                                     |  |  |

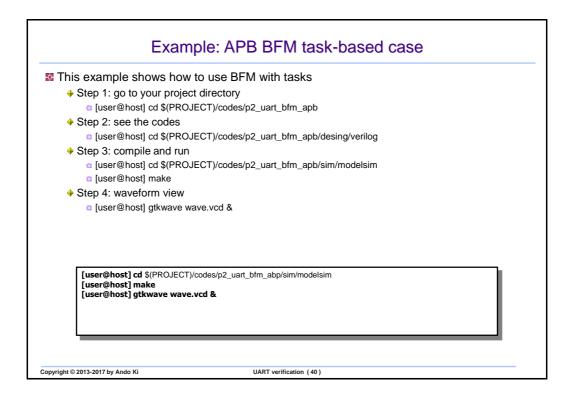

| lss                              | sues, project and quiz |  |

|----------------------------------|------------------------|--|

| How to use interrupt             |                        |  |

| How to implement parity in T     | TTY model              |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

|                                  |                        |  |

| Copyright © 2013-2017 by Ando Ki | UART verification (41) |  |