```

单选题

```

```

1、Assign a = (b[15:0] == 16'hd5)? 1'b0: 1'b1;该语句需要几个 4 输入 LUT 实现()

C 4

A 2

B 3

2、#include <stdio>

Main()

int a;

int b;

a = -2;

b=0;

while(a++&&++b);

printf("%d,%d\n", a,b);

程序运行后的输出结果是

A 1. 3

B 0, 2

C 0. 3

3、大规模可编程器件主要有 CPLD 和 FPGA 两类,下面对 CPLD 结构和工作原理描述中,不正确的

是( )

A CPLD 中文全称是复杂可编程逻辑器件

B基于 SRAM 的 FPGA 器件,每次上电须进行一次配置

C CPLD 的触发器资源丰富

D CPLD 信号通过芯片的延时时间是确定的

```

- 4、综合是 EDA 设计的关键步骤, 下面有关综合的描述错误的是(

- A 综合就是把抽象设计中的一种表示转换成另一种表示的过程。

- B 综合就是将电路的高级语言转换成低级的,可与 FPGA/CPLD 相映射的功能网表文件。

- C 为实现系统的速度、面积、性能要求,需要对综合加以约束,成为综合约束。

- D 综合可以理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

- 5、Y(A,B,C) = Σm(0,1,2,3)逻辑函数的化简式为( )

A Y=AB+BC+ABC

BY=A+B

C Y = A'

DY=B

6、以下代表异或门的是()

- 7、FPGA 设计优化主要考虑面积优化和速度优化,以下不属于面积优化的是( )

- A 流水线设计

- B 逻辑优化

- C串行化

- D 资源共享

- 8、设有定义: int x[2][3]; 则以下关于二维数组 x 的叙述错误的是( )

- A x[0]可以看作是由 3 个整型元素组成的一维数组

- B x[0]和 x[1]是数组名,分别代表不同的地址常量

- C 数组 x 包含 6 个元素

- D 可以用语句 x[0]=0; 为数组所有元素赋初值 0

埴空颢

- 9、时序设计的本质是满足每一个触发器的\_\_\_\_\_和\_\_\_\_的要求。

- 10、在 C 语言中,若有定义语句 int b=2;则表达式(b<<2)/(3||b)的值是\_\_\_\_。

- 11、4 输入查找表可以堪称一个有 4 位地址线的\_\_\_\_x1 的 RAM.

- 12、如果 DFF 的 hold 时间不满足,通常可以通过降低时钟运行速度来解决。

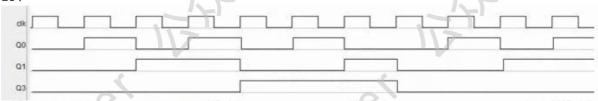

13、

上图所示计数器为进制计数器。

14、逻辑函数 F=A'B'C'D'+A+B+C+D=\_\_\_\_。

## 问答题

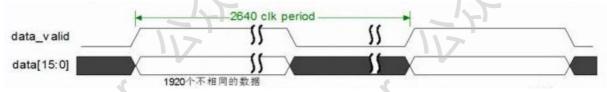

15、假设两个异步时钟  $clk_a$  和  $clk_b$ ,  $clk_a=148.5M$ ,  $clk_b=140M$ 。如图所示, $clk_a$  时钟域中连续 1920 个 16bit 的数据通过  $data_valid$  标记,有效数据之后,紧接着 720 个无效数据时钟周期。请问,该数据通过异步 fifo 同步到  $clk_b$  时钟域,异步 fifo 的最小深度是多少?请写出计算过程。

16、请用你熟悉的 HDL 语言,实现算法 Q=K\*(D-16),其中输入数据 D 和输出数据 Q 的数值定义均为无符号 8 位整数 u.8.0(无符号,8 位整数,0 位小数),输入参数 K 的数值定位为有符号数小数 s.2.10(1 位符号位,2 位整数位,10 位小数位)。要求中间过程保留完整精度,最后四舍五入。

17、一个系统有两个时钟域的电路,其时钟频率分别为 fClka=60MHz 和 fClkb=20MHz。Clka 时钟域驱动一个脉冲信号 pulsea(位宽 1bit),传输到 Clkb 时钟域的电路中,用于触发 b 模块的某些动作。电路模型和关键时序如下图。请写出 a2b 模块的 rtl 代码,并给出评估,你的设计大约用了多少个寄存器?设计中请用异步低复位。

polis\_200 polis\_300 polis\_3 THE WAR CO.